How to design with extensibility in mind?

The main issue in the design of E/E architectures is that the most important design choices pertaining to the topology and the technologies (i.e., processors, protocols, data rate, hardware) have to be made at a time when the workload, in terms of tasks and communication needs, and associated requirements (performance, safety, security, energy consumption, etc) are not entirely known.

It has been the case for years as much of the software become available later in the development process, and as new variants of a platform are progressively introduced during its lifetime. But in today’s vehicles (and most likely in aircrafts too in the future), the software will be much more frequently and importantly updated; to an extent that has not been seen before, with a plethora of new services being deployed aftermarket. The business model of OEMs will increasingly be depending on their technical capability to deploy new functions on an existing E/E architecture. For that reason, E/E architecture, and specifically communication architectures, the focus of this post, must now be as “future-proof” as possible.

The Service Oriented Architecture paradigm, whose implementation is made possible in the automotive domain by the Some/IP protocol or DDS, brings a lot of flexibility in software update implementation and associated business model. Probably OEMs will try to remain the single entry point for new services (see [1]), even if those services have been developed and are operated by third-parties. However, for the less critical services, e.g. related to infotainment, and given the weight of players like Google with their Android Auto and cloud infrastructure, it is very possible that other solutions are implemented.

Enveloppes, virtual functions and sensitivity analysis

Now, how to make sound design decisions with an imperfect knowledge of the applications the E/E will have to support? Here are some approaches which have been used in the past:

- Considering a “enveloppe” of all conceivable needs, for instance a car with all options available to clients (even if some options are incompatible). It used function OK, but it is no longer appropriate to today’s setting, as not all options / services are known at design time,

- Considering “virtual” functions, messages or ECUs: the design is conducted provisioning for some functions / messages / ECUs which are not present yet but will be introduced during the lifetime of the architecture. It is well suited when we know that the E/E architecture will have to support several successive evolutions of a platform (e.g., phase I, phase II) and when the roadmap in terms of new functions / innovation is reasonably well known,

- Sensitivity analysis: the idea is to progressively increase the load on a network or on a processor, and to identify the threshold at which performance constraints start being violated. For instance, considering today’s CAN bus with a load of 55%, assuming the traffic characteristics will remain unchanged in the future, how far can it go? Is it 70 or 90%? This approach, though coarse grained, is still useful to get an estimate of the extent to which a resource will be able to cope with an increased workload, and to identify “bottleneck resources”. An implementation of this approach is available as the ScaleLoad function for CAN (FD,XL) buses in RTaW-Pegase.

Topology Stress Test: design-space exploration on synthetic yet realistic networks

Now, how to make sound early-stage design decisions with imperfect knowledge is our focus at Cognifyer, and we have been exploring other approaches, more automated and more fine-grained in terms of the information they provide to the designers. A function available in the generative-design module of RTaW-Pegase is the Topology-Stress-Test (TST) function for Ethernet TSN. What TST does is measure the “total capacity” of a network configuration in terms of the number of streams it can support. This is performed by Monte-Carlo simulations conducted on synthetic networks of increasing loads. The capacity is expressed in probabilistic terms, e.g. “the network capacity is 200 flows at the 99% safety level” means that in 99 cases out of 100, the architecture will be able in the future to meet the performance requirements of 200 flows. The capacity of an Ethernet TSN network depends on the layout of the network, the data rates, the hardware performance, but also on the set of protocols used: priorities, frame preemption (802.1Qbu), time-triggered communication (IEEE802.1Qbv), Credit-Based-Shaping (IEEE802.1Qav), etc. TST provides the capacity for each design variants selected and each safety level selected, generating visual and textual abacuses that the designers can use to support their actual design choices.

The results of TST are valid as long as the assumptions on the communication needs are realistic. The synthetic networks are random, yet they should be created with all the knowledge the designers possesses. Capturing this knowledge is done with different input templates, chosen based on the level of knowledge the designer has on the streams and the allocations of functions. In practice, the characteristics of streams (audio, video, control, etc) tend to be well known but their proportion is often more unsure. That is why a wide range of “possible futures” is considered by TST, typically several hundred of thousands of network configurations are analyzed during a TST run.

TST was first field-tested for Renault Group’s FACE SOA E/E architecture. We showed that, in the specific context of FACE, adding a single 100Mbit/s link allows to increase by 54% the number of Some/Ip services that the architecture successfully supports, reaching 670 services at the 90% safety level with the Credit-Based-Shaping. Further details in the slides of this joint work with Renault Group presented at the 2019 IEEE Standards Association (IEEE-SA) Ethernet & IP @ Automotive Technology Day, Detroit, Mi, September 23-25, 2019 – download presentation slides here.

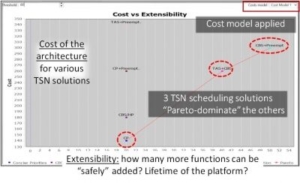

TST was then applied in a joint work with BMW presented at the Ethernet & IP @ Automotive Technology Day, 2020 – download presentation slides here in which we explore the ability of algorithmic tools to synthesize Ethernet-based architectures based on a minimal fixed core Ethernet TSN topology, design goals, design constraints, assumptions about next generation applications and data from past projects capturing part of the OEM domain knowledge. The figure below shows Pareto-optimal cost/extensibility trade-offs of different E/E architecture candidate solutions.

TST has also been successfully applied in the aerospace. For instance, a study with Airbus Helicopters presented at DACS2021 (download paper, download presentation slides here) reports on the use of TST to quantify the evolutivity of a next-generation avionics network equipped with different sets of TSN mechanisms. This study concludes that, for the specific type of systems under study, sophisticated TSN mechanisms may not be needed for next generation communication architectures.

Beyond bottleneck identification, proposing solutions

TST serves as a basis for a set of higher level generative-design functions developed at Cognifyer. One such function is “Topology Optimizer”, which goes beyond identifying bottlenecks by proposing local/incremental improvements that make a difference in terms of the network capacity, and thus, ultimately, in terms of how long an E/E architecture will remain operational. Topology Optimizer not only propose solutions to increase the capacity of an architecture, it also provide solutions to cost-optimize the architecture: link speed reduction (1Gbit/s to 100Mbit/s) wherever feasible, and removing ECUs by relocating their functions into other ECUs. Another dimension addressed by Topology Optimizer is reliability: based on fault-injection evaluation it applies “patterns of dependability” to the architecture: frame replication, link redundancy, etc. The use of Topology Optimizer to progressively cost-, capacity- and safety-optimize a next-generation zone-based architecture was exemplified in a joint work with Volvo Cars at the Automotive Ethernet Congress, 12-13 February 2020@Westin Grand Munich. – download presentation slides here.

Are you interested to know more? You are most welcome to contact us.

[1] Matthias Traub (BMW), “High-Performance Computing Architectures for Automotive”, Global Semiconductor Alliance Executive Forum 2019, Munich.